#Dsp builder matlab verification

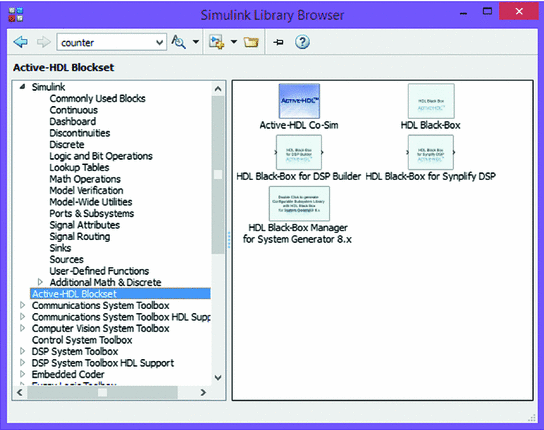

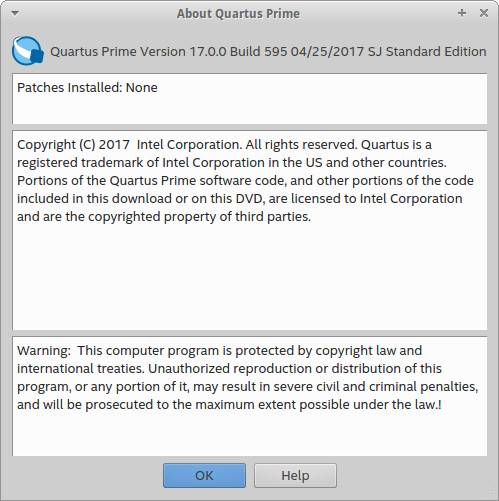

Wa_cq_url: "/content/Subscribe Send FeedbackĢ Contents Contents 1 About DSP Builder for FPGAs DSP Builder for Intel FPGAs Features DSP Builder for Intel FPGAs Design Structure DSP Builder for Intel FPGAs Libraries DSP Builder for Intel FPGAs Device Support DSP Builder for Intel FPGAs Advanced Blockset Getting Started Starting DSP Builder in MATLAB* Browsing DSP Builder Libraries and Adding Blocks to a New Model Browsing and Opening DSP Builder Design Examples Creating a New DSP Builder Design with the DSP Builder New Model Wizard DSP Builder Menu Options DSP Builder New Model Wizard Setup Script Parameters Simulating, Verifying, Generating, and Compiling Your DSP Builder Design DSP Builder Design Flow Implementing your Design in DSP Builder Advanced Blockset Dividing your DSP Builder Design into Subsystems Connecting DSP Builder Subsystems Creating a New Design by Copying a DSP Builder Design Example Vectorized Inputs Verifying your DSP Builder Advanced Blockset Design in Simulink and MATLAB Verifying your DSP Builder Advanced Blockset Design with a Testbench Running DSP Builder Advanced Blockset Automatic Testbenches Using DSP Builder Advanced Blockset References Setting Up Stimulus in DSP Builder Advanced Blockset Analyzing your DSP Builder Advanced Blockset Design Exploring DSP Builder Advanced Blockset Design Tradeoffs Bit Growth Managing Bit Growth in DSP Builder Advanced Blockset Designs Using Rounding and Saturation in DSP Builder Advanced Blockset Designs Scaling with Primitive Blocks Changing Data Type with Convert Blocks and Specifying Output Types Verifying your DSP Builder Advanced Blockset Design in the ModelSim Simulator Automatic Testbench DSP Builder Advanced Blockset ModelSim Simulations Verifying Your DSP Builder Design in Hardware Hardware Verification Hardware Verification with System-in-the-Loop Integrating Your DSP Builder Advanced Blockset Design into Hardware DSP Builder Generated Files DSP Builder Designs and the Quartus Prime Project Interfaces with a Processor Bus Primitive Library Blocks Tutorial Creating a Fibonnaci Design from the DSP Builder Primitive Library Setting the Parameters on the Testbench Source Blocks Simulating the Fibonnaci Design in Simulinkģ Contents 4. Hello, I would want to use DSP builder with Matlab, I have installed the web edition of Quartus12-SP2 and DSP builder. The fast Fourier transform library contains common blocks. This library contains basic blocks that allow you to control your design flow and run external synthesis and simulation tools. Libraries The DSP Builder Advanced Blockset comprises six libraries: Base library. Wa_audience: "emtaudience:business/btssbusinesstechnologysolutionspecialist/developer/fpgaengineer", simulation and can be accessed in the MATLAB Help for each block. Wa_english_title: "DSP Builder for Intel® FPGAs", Wa_subject: "emtsubject:itinformationtechnology/enterprisecomputing/programmablelogic", The ASK,PSK and FSK modulators and demodulators system is simulated using MATLAB/SIMULINK environment ,DSP Builder and Quartus II.

Wa_emtsubject: "emtsubject:itinformationtechnology/enterprisecomputing/programmablelogic", ASK, PSK, FSK, DSP Builder, FPGA ABSTRACT This paper present the review on an implementation of ASK, PSK and FSK modulators and demodulators on FPGA using Quartus II software. Wa_emtcontenttype: "emtcontenttype:donotuse/webpage/landingpage",

Automatically generate projects or scripts for the Intel® Quartus® Prime Software, Timing Analyzer, Platform Designer (formerly Qsys), and ModelSim*-Intel® FPGA Edition.DSP Builder by Peter Markowski, Envelope Power, Chebeague Island, Maine.

#Dsp builder matlab software

Generate resource utilization tables for all designs without a Intel® Quartus® Prime Software compile. Power Supply Control With FPGAs: Model-Based Design With Matlab, Simulink And.

Build custom arithmetic logic unit (ALU) processor architectures from a flat data-rate design with ALU folding.Perform push-button design migration to Intel's hard floating-point DSP block in Intel® Arria® 10 and Intel® Stratix® 10 devices.Perform high-performance fixed- and floating-point digital signal processing (DSP) with vector processing, such as complex IEEE 754 single-precision floating point.Go from high-level schematic to low-level optimized VHDL targeted for Intel® FPGAs.